CSE 30321 - Lecture 17 - 1st half review 172 A common An important idea... denominator  $\frac{Instructions}{\Pr ogram} \times \frac{Clock \ cycles}{Instruction} \times \frac{Seconds}{Clock \ Cycle} = \frac{Seconds}{\Pr \ ogram} = CPU \ time$ • We can see CPU performance dependent on: - Clock rate, CPI, and instruction count • CPU time is directly proportional to all 3: - Therefore an x % improvement in any one variable leads to an x % improvement in CPU performance But, everything usually affects everything: **Clock Cycle** Instruction Hardware Compiler Count Time Organization ISAs Tech. Technology CPI More in Lab 05

**University of Notre Dame**

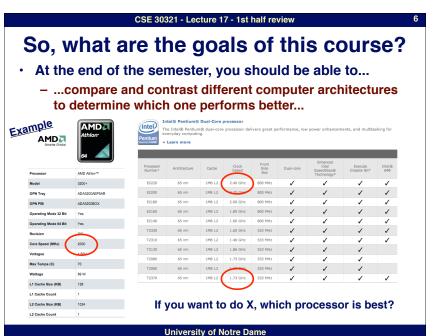

CSE 30321 - Lecture 17 - 1st half review So, what are the goals of this course? • At the end of the semester, you should be able to ... - ...design a processor architecture to meet a specific performance target... Example Find by Feature Find by Feature AMD Athlon™ X2 Dual-Cor AMD Athlon™ X2 Dual-Con Model Number 64004 lodel Numbe 5600 Frequency (MHz Frequency (MF 2900 512 L2 Cache Size (KB) 1024 L2 Cache Size (KB) AM2 Socket Socket F3 Stepping G2 Stepping Manufacturing Tech (CMOS 90nm SO Manufa 65nm SOI 125 W 65 W Wattage (W) Watta

8

2000

No

AMD Business Class

You might choose to add more or less on-chip memory...

2000

No

System Bus (MHz)

AMD Business Class

University of Notre Dame

## CSE 30321 - Lecture 17 - 1st half review

## So, what are the goals of this course?

- At the end of the semester, you should be able to...

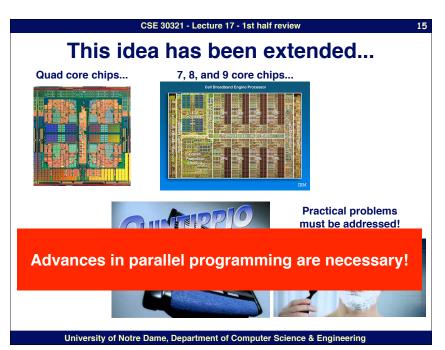

- ...explain and articulate why modern microprocessors now have more than 1 core...

- Why?

- For 8, 16 core chips to be practical, we have to be able to use them

- Students in this class should go on to play a role in making such chips useful...

**University of Notre Dame**

<text><text><text><text><text><text>

High art meets high-tech.

project, titled "CUBE," is a 10" x 10" translucent st

Top 5 Must-Haves

## CSE 30321 - Lecture 17 - 1st half review

## Solution?

(i.e. 1 processor, 1 ns clock cycle vs.

2 processors, 2 ns clock cycle)

University of Notre Dame, Department of Computer Science & Engineering

14